2.5 仿真工具Active-HDL

FPGA设计里还有一个重要的步骤就是仿真,Diamond软件开发环境同时集成了Active-HDL工具,下面看看如何进行功能仿真。

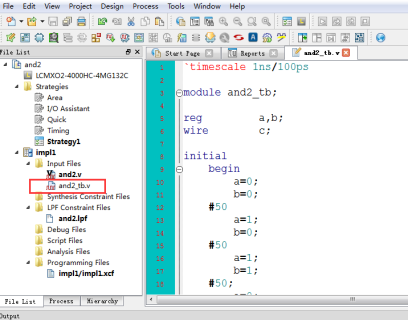

1、首先新建一个testbench文件,方法和新建Verilog源文件一样。我们命名为and2_tb.v。

2、testbench测试文件内容如下:

`timescale 1ns/100ps

module and2_tb;

reg a,b;

wire c;

initial

begin

a=0;

b=0;

#50

a=1;

b=0;

#50

a=1;

b=1;

#50;

a=0;

b=1;

end

and2 and2_u1(

.a (a),

.b (b),

.c (c)

);

endmodule

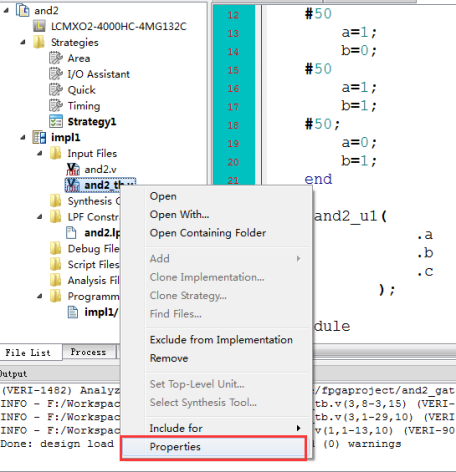

3、这里需要注意的是测试文件只是用来仿真的,很多语句是不可综合的,所以要设置文件的属性。在工程目录里右键点击and2_tb文件,

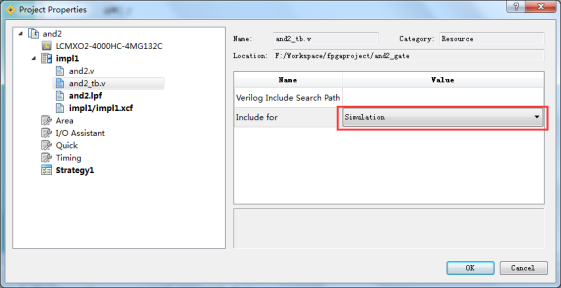

弹出一个属性窗口,把测试文件属性值改为simulation表示只做仿真。

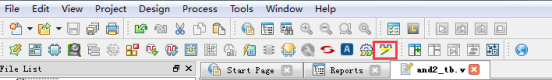

4、点击工具栏的仿真向导按钮,

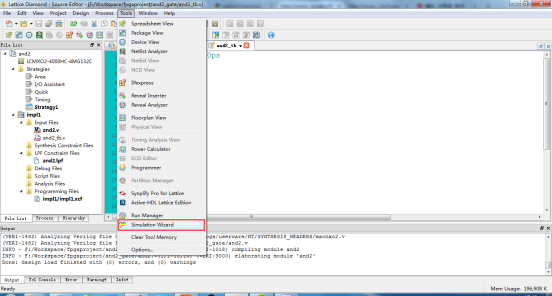

或者是Tool->Simulation Wizard

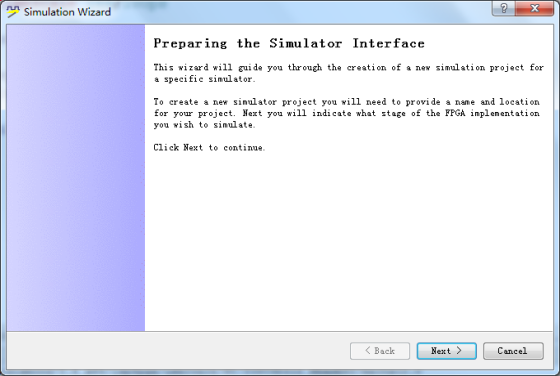

5、弹出仿真向导窗口,

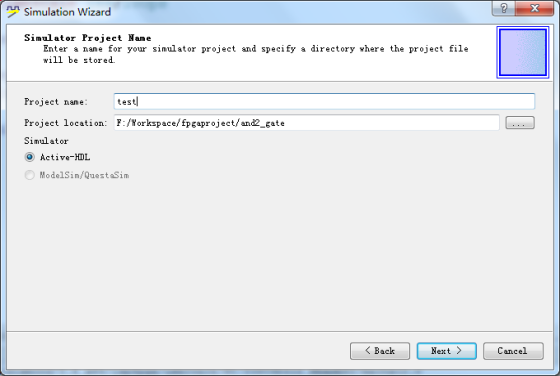

6、给仿真的工程去一个名字,

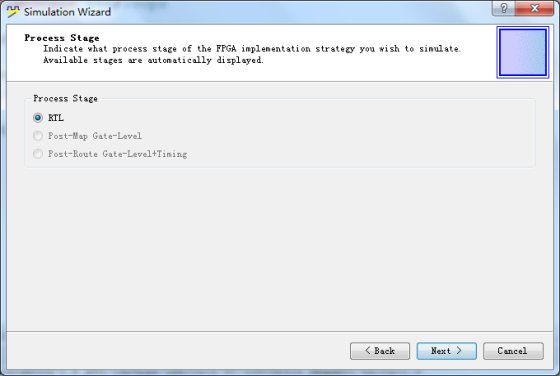

7、选择仿真的阶段,这里是功能仿真,所以只能选RTL级。

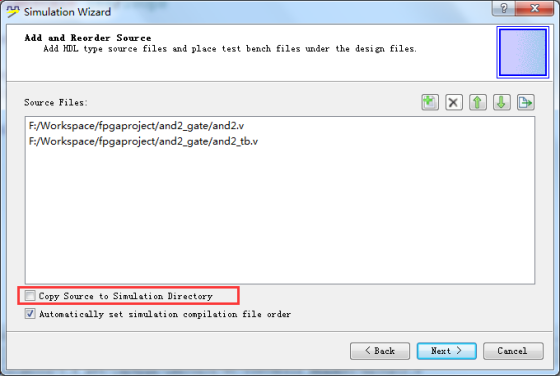

8、选择添加或者删除所要仿真的源文件和测试文件,如果确认了Copy Source to Simulation Directory选项,将会拷贝源文件到仿真工程目录。

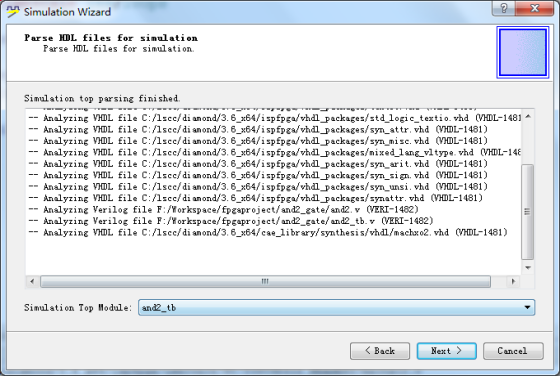

9、仿真工程列表,如果有多个测试文件可以选择顶层测试文件。

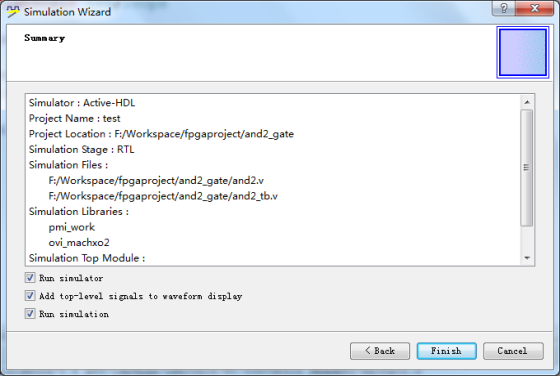

10、仿真工程项目创建完成,如果下方选项确定,将会在完成后自动执行仿真并显示波形文件。

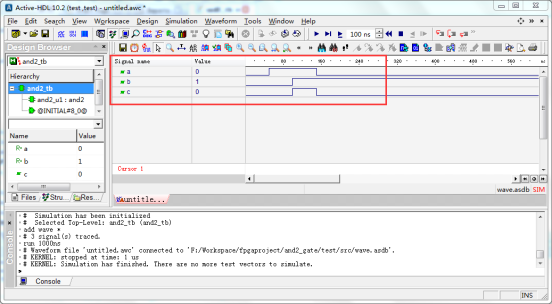

11、完成仿真向导后,执行仿真显示仿真后波形。